by Anhalt University of Applied Sciences and Perm National Research Polytechnic University

# **Proceedings of the International Conference on Applied Innovations in IT**

Eduard Siemens (editor in chief) et al.

# Proceedings of the International Conference on Applied Innovations in IT

Eduard Siemens (editor in chief) et al.

This volume contains publications of the International Conference on Applied Innovations in IT (ICAIIT), which took place in Koethen March 27th 2014. The conference is devoted to problems of applied research in the fields of automation and communications. The research results can be of interest for researchers and development engineers, who deal with theoretical base and the application of the knowledge in the respective areas.

Proceedings of the International Conference on Applied Innovations in IT, 2014.

editors: Prof. Dr. Eduard Siemens\* (editor in chief), Dr. Bernd Krause\*, Dr. Leonid Mylnikov\*\* (\*Anhalt University of Applied Sciences, \*\* Perm National Research Polytechnic University)

Copyright © Anhalt University of Applied Sciences (Hochschule Anhalt)

Volume 2, Issue 1, March 2014, Serial Number 2, 1-2014

ISBN 978-3-86011-071-3 (Online) ISSN 2199-8876

### Content

| Secti | on 1. Communication Technic<br>Dmitrii Dugaev, Eduard Siemens:                        |

|-------|---------------------------------------------------------------------------------------|

|       | A Wireless Mesh Network NS-3 Simulation Model: Implementation and                     |

|       | Performance Comparison With a Real Test-Bed 1                                         |

|       | Irina Fedotova, Eduard Siemens:                                                       |

|       | System Time Issues for the ARM Cortex A8 Processor                                    |

|       | Danijela Efnusheva, Natasha Tagasovska, Aristotel Tentov and Marija Kalendar:         |

|       | Efficiency Comparison of DFT/IDFT Algorithms by Evaluating Diverse                    |

|       | Hardware Implementations, Parallelization Prospects and Possible Improvements         |

|       | Dmitry Kachan, Eduard Siemens:                                                        |

|       | Comparison of Contemporary Protocols for High-speed Data Transport                    |

|       | via 10 Gbps WAN Connections                                                           |

|       | Bojan Gruevski, Aristotel Tentov and Marija Kalendar:                                 |

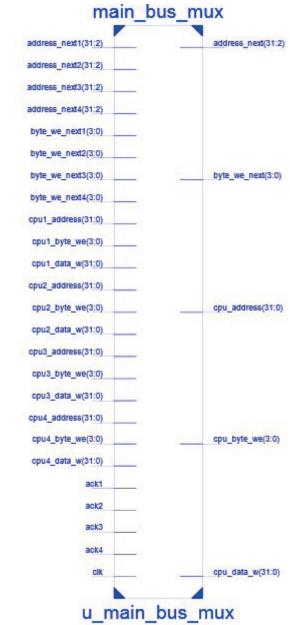

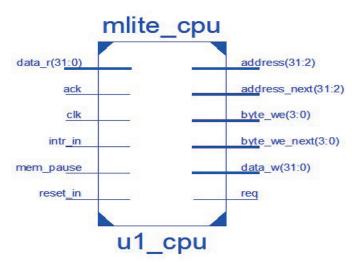

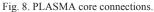

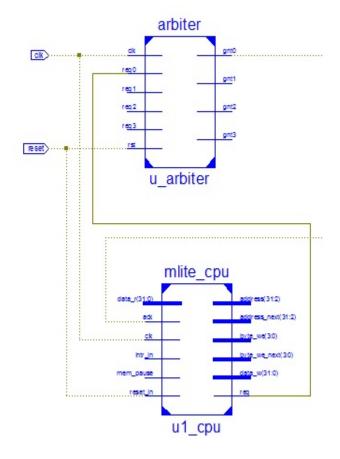

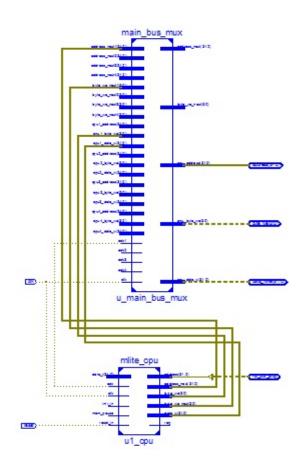

|       | Implementation of Multi-Core Processor Based on PLASMA (Most MIPS I) IP Core 29       |

|       | Anton Merkulov, Viatcheslav Shuvalov:                                                 |

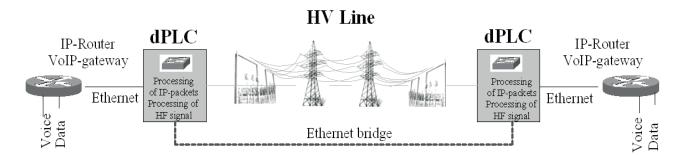

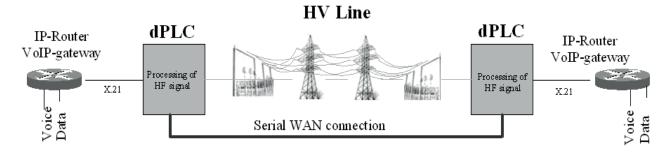

|       | The Research of Increase of Channel Efficiency for IP Traffic Transmission            |

|       | over Digital Power Line Carrier Channels                                              |

|       | Maya Malenko:                                                                         |

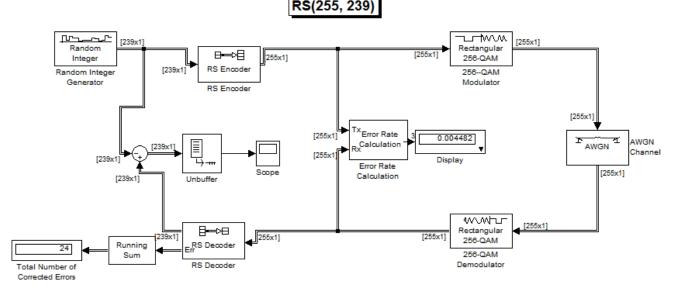

|       | Implementation of Reed-Solomon RS(255,239) Code                                       |

|       | Tatyana Chavdarova:                                                                   |

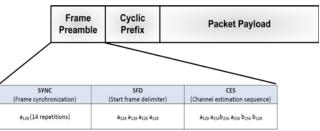

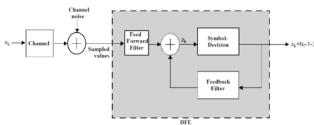

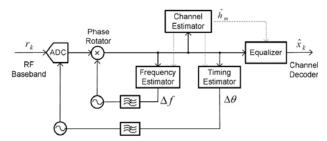

|       | Parallel Archetecture Prototype for 60 GHz High Data Rate Wireless                    |

|       | Single Carrier Reciever                                                               |

|       | Anton Merkulov:                                                                       |

|       | Assessment of the VoIP Trasmition Quality over Digital Power Line Carrier Channels 57 |

|       | Hao Hu, Dmitry Kachan, Eduard Siemens:                                                |

|       | Improving TCP Performance on CSMA/CA Connections                                      |

### Section 2. Automation and algorithms

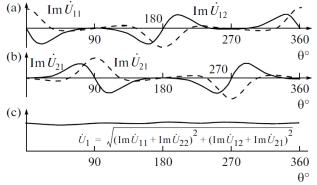

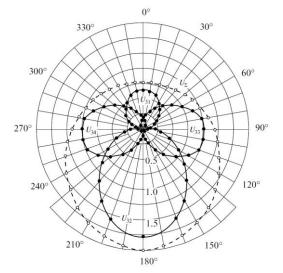

| <i>Evgeny Yakimov, Alexander Goldshtein, Valery Bulgakov, Sergey Shipilov:</i><br>Data Processing at the Flaw Detector with Combined Multisector |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Eddy-Current Transducer                                                                                                                          |

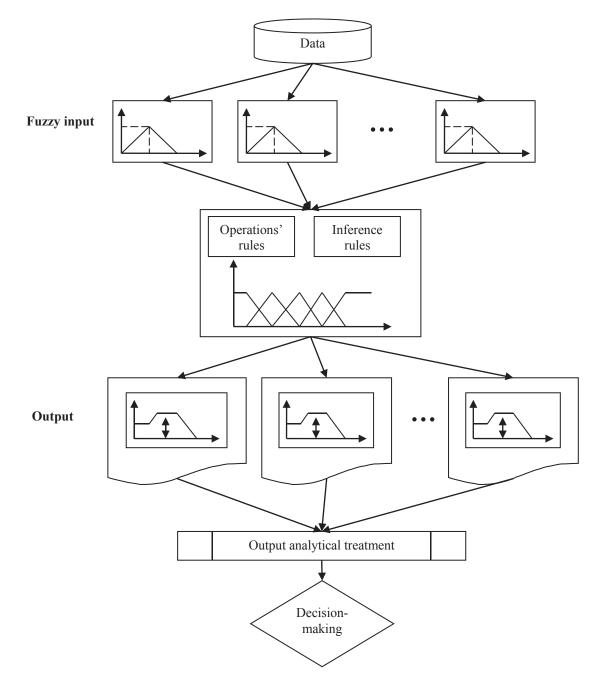

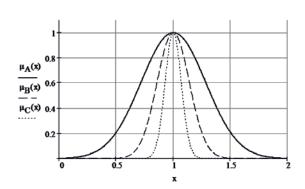

| <i>Leonid Mylnikov:</i><br>Application of Fuzzy Variables for Systems of Management Decision Support                                             |

| Anton Petrochenkov:<br>Regarding to Implementation of Genetic Algorithms in Life Cycle Management<br>of Electrotechnical Equipment               |

| <i>Igor Shmidt:</i><br>Storing Data in the Trial of Complex Technical Products                                                                   |

# A Wireless Mesh Network NS-3 Simulation Model: Implementation and Performance Comparison With a Real Test-Bed

Dmitrii Dugaev, Eduard Siemens

Anhalt University of Applied Sciences - Faculty of Electrical, Mechanical and Industrial Engineering Bernburger Str. 57, 06366 Koethen, Germany E-mail: {d.dugaey, e.siemens}@emw.hs-anhalt.de

Abstract-Wireless mesh networks present an attractive communication solution for various research and industrial projects. However, in many cases, the appropriate preliminary calculations which allow predicting the network behavior have to be made before the actual deployment. For such purposes, network simulation environments emulating the real network operation are often used. Within this paper, a behavior comparison of real wireless mesh network (based on 802.11s amendment) and the simulated one has been performed. The main objective of this work is to measure performance parameters of a real 802.11s wireless mesh network (average UDP throughput and average one-way delay) and compare the derived results with characteristics of a simulated wireless mesh network created with the NS-3 network simulation tool. Then, the results from both networks are compared and the corresponding conclusion is made. The corresponding results were derived from simulation model and real-world test-bed, showing that the behavior of both networks is similar. It confirms that the NS-3 simulation model is accurate and can be used in further research studies.

*Keywords*: wireless mesh networks, 802.11s, HWMP, network simulation, NS-3.

#### I. INTRODUCTION

A concept of wireless mesh networks (WMN) has become popular among academic researchers and telecommunication industry within the last decade. The most attractive property of such networks is a possibility of rapid and cost-effective deployment of networks with ability to provide high-capacity services for an end-user. Moreover, a diversity of wireless mesh networks applications is very wide, making it a convenient solution to use them in various projects in diverse areas, such as transport (VANET) [1], military civil and communication infrastructures, environment and public safety [2][3].

At Anhalt University of Applied Sciences (HSA), the Future Internet Lab Anhalt (FILA) is currently conducting a couple of projects with extensive usage of wireless mesh technologies. During the implementation stage of these projects, a question of adequate performance evaluation of WMN arises. As a solution of this problem, a networking simulation environment NS-3 is proposed to be used [4]. Based on the simulation, it is possible to imitate, run and to see a network behavior with any topology, size, mobility, wireless medium parameters and traffic profiles and intensity. To do that, we need to implement a simulation environment, which behavior will be adequate and comparable to a behavior of a real wireless mesh network under real conditions. This is the main objective of this paper.

For a real-world test-bed, a 802.11s wireless mesh networking standard [5] has been used – an open80211s Linux implementation [6], in particular. For the simulation model – an NS-3 networking simulator with implemented 802.11s MAC-layer stack [7] is chosen. As for performance parameters – an average UDP throughput and an average delay will be evaluated in both test-bed and simulation model.

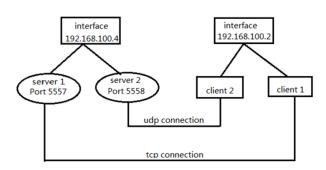

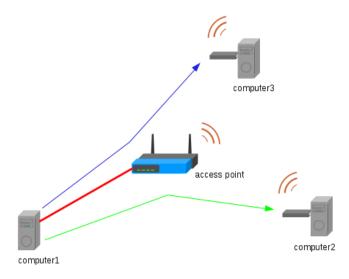

#### A. Test-bed description

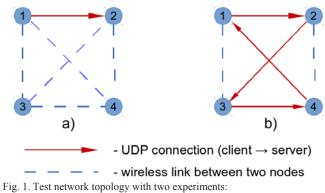

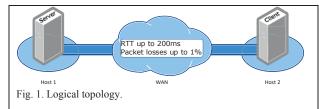

To be able to compare parameters of the simulated network with a real-world scenario, a test-bed network has been deployed. The network consists of 4 wireless nodes placed in 2x2 grid topology with a distance between them equals to 1 meter. The topology of the test network is illustrated on Fig.1.

As the network's node, an ARM-based system-on-chip (SoC) had been used with a wireless 802.11 adapter based on rt2800 mesh-compatible driver [8]. Then, a Linux OS with modified kernel and the open80211s [6] implementation of the mesh standard has been installed on the SoC [9] (as in Fig. 2).

A mesh mode was switched on with HWMP routing protocol with default Airtime Link routing metric [10], equation (1):

$$c_a = \left[O + \frac{B_t}{r}\right] \cdot \frac{1}{1 - e_f},\tag{1}$$

where

$c_a$  – the airtime cost;

O - a constant, which defines a channel access time depending on the used physical implementation (802.11a, 802.11b);

B<sub>t</sub> – test packet size (8192 bits);

r – channel data rate (Mbps);

e<sub>f</sub> – packet error probability.

a – 1 UDP connection;

b-4 simultaneous UDP connections.

To evaluate r and  $e_f$  values, a node sends a block of test packets. The length of the test packet is a default value which is set by the standard – 8192 bits.

In a case of independent packet errors, the packet error probability can be calculated as (2):

$$e_f = 1 - (1 - p_o)^n \approx n p_o, \tag{2}$$

where

p<sub>0</sub> – transmission bit error probability;

n – number of bits being transmitted.

#### B. Simulation description

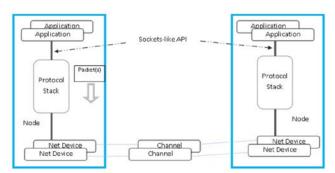

For the simulation purposes, NS-3 network simulator has been used [4] [11]. NS-3 is a discrete-event simulator with a special focus on Internet-based systems, consisting of different library components (core, simulation, node libraries, physical and channel models, network routing protocols implementations, etc.) written in C++. Such structure allows researchers to modify, adjust and simulate various networking scenarios. The general simulation architecture of NS-3 [11] is depicted on Fig. 3.

In order to simulate the real-world test-bed as accurate as possible, a few main network characteristics must match:

- the same 2x2 grid static topology;

- propagation loss model;

- physical interference model;

- modulation scheme and the frequency range (802.11g, 6Mbps OFDM rate);

- 802.11s peer-link management protocol and HWMP parameters;

The 802.11g modulation standard has been used in both simulation and real test-bed since this is the most recent specification which is supported by the current 802.11s

Fig. 3. NS-3 main simulation objects.

| IP                       | IP               |  |  |  |  |  |  |  |  |  |

|--------------------------|------------------|--|--|--|--|--|--|--|--|--|

| 802.1 bi                 | ridging          |  |  |  |  |  |  |  |  |  |

| 802.11 station 802.11 AP | 802.11s mesh STA |  |  |  |  |  |  |  |  |  |

| mac80211                 | open80211s       |  |  |  |  |  |  |  |  |  |

| Hardwar                  | e driver         |  |  |  |  |  |  |  |  |  |

Fig. 2. The open80211s stack integrated into the Linux kernel.

implementation (open80211s). The 802.11n standard is not supported yet by mesh devices.

HWMP stands for Hybrid Wireless Mesh Protocol, which is used as a default multi-hop routing scheme in 802.11s standard.

One of the important parameters used in the simulation is the chosen propagation loss model which should consider the real-world wireless medium irregularities such that various obstacles (walls, doors, people, etc.) and interferences (electrical equipment, other wireless systems, etc.). These factors decrease the signal strength in different ways.

In NS-3, there are several available propagation loss models [11]: fixed RSS loss model, Friis propagation loss model, Jakes propagation loss model, Nakagami propagation loss model, random propagation loss and log distance propagation loss models. They are used in different wired and wireless communication scenarios.

For our case, where the distance between the nodes is short and static, and the measurements are conducted in a building, the Log-Distance Propagation Loss Model [11] was the most suitable and adaptive. This model calculates the reception power (received signal strength) using the following equation (3):

$$L = L_0 + 10 \cdot n \cdot \log_{10} \left( \frac{d}{d_0} \right), \tag{3}$$

where

$L_0$  – path power loss (signal attenuation) at reference distance (dB);

- n the pass loss distance exponent;

- d distance (m);

- $d_0$  reference distance (m);

- L path power loss (signal attenuation) (dB).

To adapt this propagation loss model to a real test-bed, correct values of these variables has to be found. A YansWifi [11] physical interference model has been used to simulate the signal's interference; a frequency range and modulation scheme have been taken from 802.11g standard with 6 Mbps bitrate. 802.11s HWMP routing parameters have been set to default values.

#### II. THE 802.11S ROUTING SCHEME

A 802.11s standard was developed by IEEE 802.11 task group in 2006 with main objective to overcome the limitations of traditional Wi-Fi star topologies (Access Point – Clients) and to enable a deployment of wireless mesh

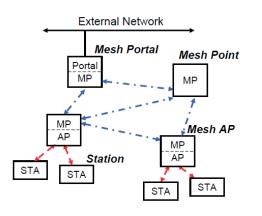

Fig. 4. A general architecture of 802.11s WMN network.

networks based on 802.11 MAC layer with layer-2 (L2) multi-hop routing scheme, provided by HWMP.

A general 802.11s based WMN architecture is shown in Fig. 4. It consists of 4 classes of devices [9]:

- Mesh Point (MP) wireless mesh node with data routing and forwarding functionality;

- Mesh Access Point (MAP) wireless mesh node with additional functionality of wireless access point (AP), allowing different wireless clients to connect to WMN;

- Mesh Portal (MPP) a gateway connecting WMN with another external networks;

- Stations (STA) wireless 802.11 devices connected to MAP;

Currently, the 802.11s standard categorizes frames as data, control and management frames. Control frames are used for exchanging acknowledgements and path reservation messages, whereas the management frames perform a function of establishing and maintaining the WMN. The 802.11s frame format provides additional mesh control fields for data routing over multiple hops, including source address (initial hop), destination address (final hop) and mesh source address [10].

#### III. HWMP PROTOCOL

Hybrid Wireless Mesh Network Protocol belongs to the class of so-called hybrid routing schemes, which means that it can work in both proactive and active modes alternatively or simultaneously.

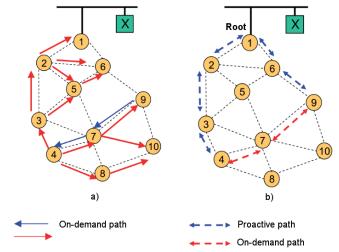

In the reactive mode (Fig. 5a), the node's forwarding table is created right before the beginning of data transmission. Upon sending the data packets, a source node sends a broadcast Path Request (PREQ) message to its neighbors which change the Air-Time Metric value and forward it further. A sink node receives the PREQ and sends back a Path Reply (PREP) message back to the source. When the source node gets the reply (PREP), it obtains the information about the whole path (path metric) and makes a transmission decision [12].

In the proactive mode (as in Fig. 5b), the wireless mesh network has to set a root node, which transmits broadcast root requests (RREQ) in order to form a path tree. In such case, every mesh node has the information about how to deliver data packets to every other node through the root beforehand.

Fig. 5. Connection establishing between nodes 4 and 9: [5] a – in HWMP reactive mode; b – in HWMP proactive mode.

#### IV. EXPERIMENT MAP

As it has been mentioned above, the test topology of the WMN (real-world test-bed and NS-3 simulation script) represent a 2x2 grid with 1 m distance between two nodes, as it is illustrated on Fig.1.

Two main performance parameters are chosen for the evaluation – average UDP throughput and average one-way delay. A network traffic load parameter (in the form of a number of simultaneous UDP connections) is chosen as a variable value.

In the real-world test-bed, the throughput value of the generated UDP traffic is estimated by the client side of the iperf utility [13] after the channel having been loaded according to its established transmission bitrate.

The average one-way delay (OWD) under different traffic loads was measured using LTest tool [14]. The LTest utility generates UDP traffic with fixed data rate and calculates one-way delay from that. However, in contrary to measurements of RTT, on OWD, a high-precision time synchronization of the corresponding CPU clocks is crucial, which is provided by LTest. This provides highly accurate one-way delay values between sender (client) and receiver (server).

The duration of each test in the real-world test-bed as well as in the simulated network has been set to 100 seconds. The UDP packet size and each client's UDP stream data rate have been set to 1024 Bytes and 6 Mbps correspondingly.

In the simulation script, the aforementioned parameters were calculated using formulas (4) and (5):

$$R_{avg} = \frac{N_{rec.bits}}{T_{lastbit} - T_{firstbit}},\tag{4}$$

where

Nrec. bits - number of received bits;

$T_{\text{last bit}}$  and  $T_{\text{first bit}}$  – time of the last and the first bits received correspondingly;

$$OWD_{avg} = \frac{T_{TOTAL}}{N_{rec.\,packets}},\tag{5}$$

where

$T_{TOTAL}$  – total transmission time; N<sub>rec. packets</sub> – number of received packets.

#### V. MEASUREMENT AND SIMULATION RESULTS

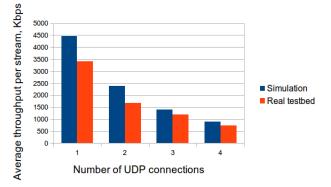

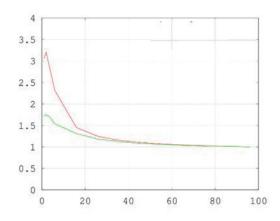

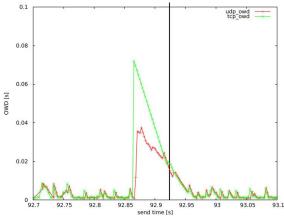

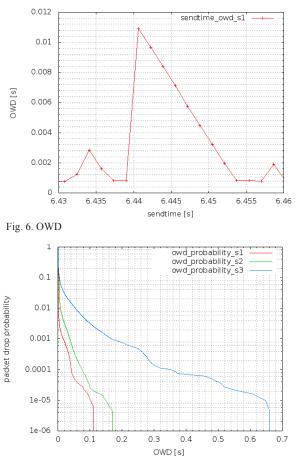

After having conducted a number of experiments, we derived the dependencies of average throughput and average one-way delay as functions of UDP traffic load (number of UDP connections each with 6 Mbps data rate). It was stated that as the traffic load increases, a common wireless mesh network decreases significantly due to physical characteristics of wireless transmission medium (noisy environment, increasing interference) and current open80211s implementation. This fact is confirmed by the NS-3 simulation, where a similar behavior is detected. In general, the simulated average throughput values correspond to the ones from the test-bed (as in Fig. 6). The absolute average throughput values in the worst case differ in about 34%, and in the best case -14%.

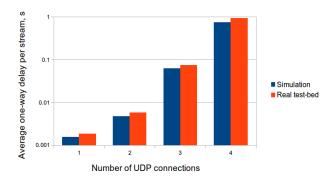

Furthermore, the average one-way delay increases as the number of UDP connections grow in both real test-bed and simulated networks with a very similar behavior. It can be explained with the fact that the 802.11s standard is mostly based on 802.11 MAC-layer which exploits CSMA/CA multiple access scheme. Therefore, with the increasing network traffic, the number of frame retransmission quickly increases, affecting the overall delay. Moreover, the current 802.11s implementation (open80211s) is still under extensive development and sometimes we were faced with unstable network behavior under very high loads. However, under medium traffic loads, the real-world test-bed network behavior is stable, which is confirmed by the simulation illustrated on Fig. 7.

The average throughput values derived from both scenarios and their percentage difference are presented in Table 1. As it can be seen from the numbers, the relative difference between the real test-bed and the simulation model does not exceed 35% in the worst case (2 UDP connections), and is equal approximately to 14% in the best case (3 UDP connections). The simulation model becomes more accurate when there are two and more simultaneous connections, which can be explained by the fact that the signal interference starts to play the most significant role in the network performance behavior, and the YansWifi signal interference model is well-implemented in NS-3 simulator.

In Table 2, the average one-way delay values and their corresponding percentage difference are presented. In this scenario, the similarity in the real test-bed and the simulation model behaviors is even better. The worst percentage difference is only 24% and the best one is 14%. In this case, it is quite difficult to establish the relation between UDP traffic intensity and the simulation model accuracy. These random fluctuations in accuracy deviations can be explained only by the randomness of wireless channel model used in NS-3 simulator and by unpredictable behavior of the real wireless medium.

Fig. 6. Average UDP throughput per stream behavior in real test-bed and simulation.

Fig. 7. Average one-way delay per stream in real test-bed and simulation.

TABLE I AVERAGE THROUGHPUT VALUES OF REAL TEST-BED AND SIMULATION, (K pps)

| (KBF3)                    |        |        |        |       |  |  |  |  |

|---------------------------|--------|--------|--------|-------|--|--|--|--|

| Number of UDP connections | 1      | 2      | 3      | 4     |  |  |  |  |

| Simulation, Kbps          | 4471.6 | 2387.8 | 1403.6 | 908.3 |  |  |  |  |

| Real test-bed,<br>Kbps    | 3415.8 | 1677.3 | 1209.3 | 744.7 |  |  |  |  |

| Percentage<br>difference  | 26 %   | 34 %   | 14 %   | 19 %  |  |  |  |  |

TABLE II Average One-Way Delay Values of Real Test-Bed and Simulation, (ms)

| Number of UDP connections | 1    | 2    | 3     | 4      |

|---------------------------|------|------|-------|--------|

| Simulation, ms            | 1.54 | 4.81 | 62.85 | 743.1  |

| Real test-bed, ms         | 1.84 | 5.84 | 73.86 | 946.34 |

| Percentage<br>difference  | 17 % | 19 % | 16 %  | 24 %   |

All in all, a discrepancy in the calculated values is acceptable and can be explained by non-ideal wireless physical medium (additional noise sources, random noise, etc.), occasional unstable behavior of open80211s implementation and wireless driver (rt2800) as well as current 802.11s model characteristics in NS-3. However, the similarity between test-bed and simulated network model is clearly seen.

#### VI. CONCLUSION

Basing on the results derived from the experiments, we can observe that the behaviors of the real test-bed and the simulated network are quite similar. It means, that the physical, interference and channel models in NS-3 simulator are set with sufficient accuracy and fit to the purposes of evaluation performance parameters of different wireless mesh networks with various topologies. Moreover, the

802.11s protocol stack (Peer Link Management protocol and HWMP) implemented in NS-3 adequately imitates hybrid routing schemes and link establishing algorithms of real wireless mesh network implementation based on open80211s.

Therefore, the experiment results allow us to conclude that the proposed NS-3 simulation model can be used for wireless mesh networks performance evaluation with satisfactory accuracy in ongoing FILA projects (SoCiEr, Smartlight) as well as in any future projects which involve wireless mesh networking communication.

#### REFERENCES

- S. Zeadally, R. Hunt, Y. Chen, A. Irwin, and A. Hassan, "Vehicular Ad Hoc Networks (VANETS): Status, Results, and Challenges," 2010.

- [2] H. Aiache, V. Conan, G. Guibe, J. Leguay, C. L. Martret, X. Gonzalez, A. Zeini, and J. Garcia, "WIDENS: Advanced Wireless Ad-Hoc Networks for Public Safety," IST summit, 2005.

- [3] A. Yarali, B. Ahsant, and S. Rahman, "Wireless Mesh Networking: A Key Solution for Emergency & Rural Applications," The Second International Conference on Advances in Mesh Networks, 2009.

- [4] NS-3 network simulator official website. [Online]. Available: www.nsnam.org

- [5] "IEEE Draft Standard for Information Technology-Telecommunications and in-formation exchange between systems-Local and metropolitan area networks - Specific requirements - Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications-Amendment 10: Mesh Networking," IEEE P802.11s/D10.0, March 2011, pp. 1–379, 29, 2011.

- [6] open80211s open-source implementation of the recently ratified IEEE 802.11s wireless mesh standard. [Online]. Available: <u>http://open80211s.org/</u>

- [7] K. Andreev and P. Boyko, "IEEE 802.11s mesh networking NS-3 model," 2009.

- [8] Existing Linux Wireless drivers. [Online]. Available: http://wireless.kernel.org/en/users/Drivers

- [9] G. Hiertz, D. Denteneer, S. Max, R. Taori, J. Cardona, L. Berlemann, and B. Walke, "IEEE 802.11s: The WLAN Mesh Standard," IEEE Wireless Communications, vol. 17, no. 1, pp. 104-111, 2010.

- [10] R. C. Carrano, L. C. S. Magalhaes, D. C. M. Saade, and C. V. N. Albuquerque, "IEEE 802.11s Multihop MAC: A Tutorial," IEEE Communications Surveys and Tutorials Volume 13, Number 1, First Quarter 2011.

- [11] NS-3 doxygen documentation. [Online]. Available: www.nsnam.org/doxygen-release/index.html

- [12] IEEE P802.11s/D1.00. Amendment: Mesh Networking. IEEE, 2006.

- [13] Iperf The TCP/UDP Bandwidth Measurement Tool. [Online]. Available: <u>http://iperf.fr/</u>

- [14] E. Siemens, S. Piger, C. Grimm, and M. Fromme, "LTest A Tool for Distributed Network Performance Measurement," Proc. Consumer Communications and Networking Conference, 2004. First IEEE. 2004, pp. 239-244.

Proc. of the International Conference on Applied Innovations in IT, (ICAIIT), Volume 2, Issue 1, March 2014

# System Time Issues for the ARM Cortex A8 Processor

Irina Fedotova, Eduard Siemens Anhalt University of Applied Sciences - Faculty of Electrical, Mechanical and Industrial Engineering Bernburger Str. 57, 06366 Koethen, Germany E-mail: <u>{i.fedotova, e.siemens}@emw.hs-anhalt.de</u>

*Abstract*—The use of system-on-chip (SoC) platforms has emerged as an important integrated circuit design trend for communication and industrial control applications. At the same time, requirements of stable, efficient and precise processing time values are growing rapidly. Since the ARM processor doesn't possess known timers of PC-platforms such as TSC counter or HPET timer, the common way to obtain time values on ARM-architecture is still only through Linux system calls which are mapped to ARM specific time counters. Indeed, direct access to hardware can help to reduce costs down to 200 nanoseconds against 2-1 microseconds of the time acquisition via Unix system call interface. However, designing this approach is a challenging task. This paper describes specific issues and features of tracking system time on the ARM Cortex A8 processor under Linux OS.

*Keywords:* timestamp precision; time-keeping; embedded Linux; ARM architecture.

#### I. INTRODUCTION

Over the last few years, the ARM architecture has become the most pervasive 32-bit architecture in the world, with wide range of integrated circuits available from various manufacturers. ARM processors are embedded in products ranging from cell/mobile phones to control systems of windturbines. Depending on the specific products [1][2][3], requirements of meeting timing constrains vary from reaction in a predefined time frame (as in the hard-real time system) and not critical timely responsiveness (as in the soft-real time system). However, any real-time requirements on ARM embedded projects can't be met without reliable development platform.

The Linux kernel offers interrupt latency less than 100 nanoseconds in most cases on today's fast processors. Although, the non-deterministic nature of task scheduling may make it unsuitable for some hard real-time systems, the wealth of utility programs included with Linux makes it ideal for such tasks as report generation as well as networking and addressing interoperability issues [4][5]. Though the Linux OS, running on diverse ARM architectures becomes increasingly popular in embedded systems, often exactly the lack of high-precision time control pushes system designers to decisions against Linux-based, towards more costly FPGA- or ASIC-based solutions

Modern PC-platforms come with different hardware timers having different attributes. The most popular in the PC domain is a 64-bit TSC counter which represents relative time values and counts CPU cycles from the power on or reset of the computer. The HPET device provides multiple timers, each consisting of a timeout register that is compared with its central counter. Meanwhile, the timing mechanism of ARM-architecture appears more complex. The time performance on ARM is limited by a 32-bit register with a relatively low frequency of 41 ns and hence, the overflow occurs in less than every 3 minutes. Additionally, ARM specific restrictions of memory management allow accessing to registers only from kernel space.

The remainder of the paper is organized as follows. In Section II, related work is described. Section III shows the specific details of each initial time source within the ARM Cortex A8 processor. Some experimental results of appropriate timer sources along with their performance characteristics are shown in Section IV. Finally, Section V describes next steps and future work in our effort to develop a tool for efficient high-performance measurements.

#### II. RELATED WORK

Since the essence and importance of time acquisition in embedded systems has become apparent, several research projects have suggested to design timing mechanism for real-time application [6][7]. However, these researches consider handling of timer on the outdated platforms, such as, for example, AVR microcontrollers. In other proposals, the entire time capturing process is integrated into dedicated hardware devices [8]. For PC-platforms based on x86 and x86-64 processors, the idea of the invention single structure providing access to different hardware timers has already been suggested [9][10]. Nevertheless, our investigations directed to specific timers of ARM-architecture with the potential purpose of designing the new accurate real-time system

#### III. ARM CORTEX A8 SPECIFIC CLOCKS AND TIMERS

All current investigations are being performed on the *BeagleBone* credit-card-sized Linux computer with single-core AM335x Cortex A8 ARM processor under the Debian GNU/Linux 7.0 with the stable kernel version 3.8.10.

On the given platform, maximum performance and operation timer for user satisfaction is ensured by the special power, reset, and clock management (PRCM) module. This module provides a centralized control for the generation, distribution and gating of most clocks in the device. PRCM gathers external clocks and internally generated clocks for distribution to the model in the device. Moreover, PRCM manages the system clock generation.

Following to the processor's technical manual [11, Chapter 8], the device has two reference clocks which are generated by on-chip oscillators or externally. These are for the main clock tree and RTC block, respectively. In the case of an external oscillator, the 32-KHz crystal oscillator is controlled and is configurable by RTC. This device also contains an on-chip oscillator. This oscillator is not configurable and is always on. The main oscillator on the device produces the master high frequency clock.

Therefore, we assume that there are oscillators with at least two different frequencies. The first one is widespread 32,768 kHz frequency, which is exactly  $2^{15}$  cycles per second, a convenient rate to use with simple binary counter circuits. In this case, the time resolution is 31,25 µsec The second value, so called master frequency, is equaled to 25 MHz with 40 nsec resolution, which allows performing comparatively fast measurements. Table 1 gives more detailed description of available clocks.

TABLE I CLOCKS RESOLUTION AND MAXIMUM RANGE

| Clock  | Prescaler | Resolution | Interrupt<br>Period Range | Wraps<br>every |

|--------|-----------|------------|---------------------------|----------------|

| 32.768 | 1 (min)   | 31.25 us   | 31.25 us to<br>~36h 35m   | 37 h           |

| KHz    | 256 (max) | 8 ms       | 8 ms to<br>~391d 22h 48m  | 57 11          |

| 25     | 1 (min)   | 40 ns      | 40 ns to<br>~171.8s       | 2.082 m        |

| MHz    | 256 (max) | 10.24 us   | ~20.5 us to<br>~24h 32m   | 2, 983 m       |

A prescaler is an electronic counting circuit, which allows the timer to be clocked at the rate user desires. The prescaler takes the basic timer clock frequency and divides it by some value before feeding it to the timer. For the given clocks, prescaler's divisor varies from 1 to 256 and accordingly provides 8 different values (divisible by two) of clock resolution. So, with every increase of clock range, the resolution is decreased.

According to the processor specification [11, Chapter 20], four possible timers exist on this processor:

- Dual Mode Timer (DMTimer);

- Dual Mode Timer 1 ms (DMTimer 1 ms);

- Real Time Clock Subsystem (RTS SS);

- WATCHDOG.

The peripheral DMTimer is 32-bit timer and the module contains a free running upward counter with auto reload capability on overflow. The timer counter can be read and written in real-time (while counting) and configured for 32bit or 16-bit operation. DMTimer can be configured in three modes of operation: timer mode, capture and compare mode. The compare logic allows an interrupt event on a programmable counter matching value. The capture mode allows capturing of the timer value in a separate register based on an input signal. By default, after core reset, the capture and compare modes are disabled.

In fact, DMTimer provides eight multiple timers:

The DMTimer0 can only be clocked from the internal RC oscillator of 32.768 KHz.

- The DMTimer1 is implemented using the DMTimer\_1ms module, which is capable of generating an accurate 1 ms tick using a 32.768 KHz clock. During low power modes, the master oscillator is disabled. Hence, in this scenario for generating the OS 1ms tick and timer based wakeup, it is sourced from the 32K RC oscillator.

- Each functional clock of DMTimer[2-7] is selected using the associated register from 3 possible sources: the 24-MHz system clock, the 32.768 KHz clock (see Table 1) or the external timer input clock. The availability of particular DMTimer[2-7] depends on the platform implementation. The Linux kernel already contains *dmtimer* driver, which allows using system time through accessing to the DMTimer2. Therefore, this timer is considered as preferable.

Additionally, as any other electronic device, the given processor possesses RTC clock, which keeps time of day, and have an alternate source of power, so that it works even with system power off. The RTC supports external 32.768kHz crystal or external clock source of the same frequency.

The processor also contains a WATCHDOG timer based on an upward 32-bit counter coupled with a prescaler. It causes the system to be reset if it is not poked periodically. After reset generation, the counter is automatically reloaded with the value stored in the watchdog load register, the prescaler is reset and the timer counter begins incrementing again.

#### IV. TIME FETCHING PERFORMANCE RESULTS

On ARM platforms, all I/O access is memory-mapped. That means that timers' registers have their specific address stored in a known private memory region and access to them potentially possible only from kernel space. The *dmtimer* driver available in Linux also does not provide high-level abstractions. It is merely a small library supplying some functions for the clients of DMTimers to reserve and program the timers. So, the clients have to manage all the low-level programming and interrupt handling themselves. Accordingly, this driver is considered not used by many.

So, the suggested way of avoiding this obstacle for user would be writing a character device driver and implement *mmap()* function and the read-only access to the timer. It will allow mapping of the physical address of the DMTimer2 main counter to a virtual address in the program memory space.

The idea of timers map is as follows: firstly, the user process invokes an appropriate mmap() function and the kernel calls the device driver passing all necessary parameters. The driver validates the request and executes a function to map the necessary range of physical addresses into the address space of the user space. The driver returns an exit code to the kernel and the kernel re-dispatches the user process. Therefore, the user process accesses data of timing hardware by accessing the virtual address returned to it from mmap() call. Herewith, inaccurate offset in timer register from user space is handled in the open device operation in kernel space and in the case of error, returns user appropriate message.

Table 2 shows the performance results of getting the time values using direct access to hardware versus using a system

call. Initially hardware timer, DMTimer2 with 25 MHz frequency was chosen. For the system call, *clock\_gettime()* was issued. For this investigation, time was fetched in a loop of 10 million consecutive runs. The values are not filtered.

TABLE II

THE COSTS OF OBTAINING TIME VALUES ON ARM PROCESSOR

| Time source                 | Mean, µsec | Standard<br>deviation, µsec |

|-----------------------------|------------|-----------------------------|

| System Call                 | 1.025      | 2.201                       |

| Direct Access<br>to DMTimer | 0.201      | 0.800                       |

Additionally, during these tests, CPU system time was estimated relatively real execution time of the program. In fact, CPU costs value of system call is more than 10 times greater than direct access to hardware.

TABLE III CPU Costs on ARM Cortex A8 Processor

| Time source                 | Real time of test execution | System time | Percentage ratio |  |  |

|-----------------------------|-----------------------------|-------------|------------------|--|--|

| System Call                 | 2m 59.203s                  | 0m 20.846s  | 11.632%          |  |  |

| Direct Access<br>to DMTimer | 2m 15.723s                  | 0m 1.303s   | 0.960%           |  |  |

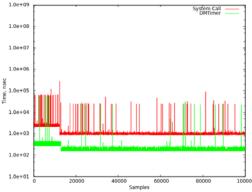

The chart in Fig. 1 demonstrates more detailed results of this experiment. The range of samples was decreased to track the behavior of timers more carefully. It shows the clear similarity of both timers' behaviors and proves that the given system interacts with this particular DMTimer2 hardware.

Fig. 1. Measurements of timers costs on the ARM Cortex A8 processor

#### V. CONCLUSION AND FUTURE WORK

With the rapid development of the field of industrial process control and the wide range of embedded systems, it is necessary to make a higher demand of the time accuracy and reliability of the control system. The embedded ARM Cortex A8 platforms can adapt to strict requirements of the time acquisition and potentially become a basis for building new real-time systems.

Nevertheless, primarily the number of significant issues must be satisfied. Firstly, the reliable interface allowing interacting with system timer must be provided, wherein the benefits of hardware access (such as low cost of obtaining values and low CPU costs) are saved. Secondly, a protection from timer 2.9 min overflow should guarantee meeting realtime constraints. Therefore, at this stage accomplishment of all above challenges is in progress. Moreover, to the next steps, the better support of the ARM Cortex A9 processor will be addressed. The potential benefits of multi-core processors for real-time embedded systems are enormous, but however have even more dangerous drawbacks.

#### REFERENCES

- M. Manivannan and N. Kumaresan, "Embedded web server & GPRS based advanced industrial automation using Linux RTOS," International Journal of Engineering Science and Technology, vol. 2 (11), no. 8, pp. 6074-6081, 2010.

- [2] D. Wiklund and D.Liu, "SoCBUS: Cwitched network on chip for hard real time embedded systems," Proc. of the 17<sup>st</sup> Intl. Symposium on Parallel and Distributed Processing, Los Alamitos, pp. 78.1, IEEE Computer Society Press, 2003.

- [3] I. Fedotova and E. Siemens, "Usage of high-precision timers in the wind turbines control systems," Supercomputers Jornal, Moscow, Publishing House SCR-Media LTD, Number 16, winter 2013.

- [4] R. Lehrbaum, "Using Linux in Embedded and Real Time Systems," Linux Journal, vol. 2000 (75), Specialized Systems Consultants, Inc., 2000.

- [5] B. Japenga, "Why Use Linux for Real-Time Embedded Systems" White paper. [Online]. Available: <u>http://www.microtoolsinc.com/</u> <u>Articles/Why%20Use%20Embedded%20Linux%20for%20Real%20T</u> <u>ime%20Embedded%20Systems%20Rev%20A.pdf</u>

- [6] A. A. Fröhlich, G. Gracioli, and J. F. Santos, "Periodic timers revisited: The real-time embedded system perspective," Computers & Electrical Engineering, vol. 37, no. 3, 365-375, May 2011.

- [7] K. G. Shin, "Real-time dynamic voltage scaling for low-power embedded operating system," Proc. of the 8<sup>st</sup> ACM Symposium on Operating Systems Principles, New York, USA, pp. 89-102, 2001, doi: 10.1145/502034.502044

- [8] A. Pásztor and D. Veitch, "PC based precision timing without GPS," The 2002 ACM SIGMETRICS international conference on Measurement and modeling of systems, Marina Del Rey California, USA, vol. 30, no. 1, pp. 1-10, June, 2002, doi: 10.1145/511334.511336.

- [9] A. Aust, J. Brocke, F. Glaeser, R. Koehler, S. Kubsch, and E. Siemens, "Method for processing time values in a computer or programmable machine," US Patent 8, 185, 770, 2012.

- [10] I. Fedotova, E. Siemens, H. Hu. "A high-precision Time Handling Library," Proc. of the 9th International Conference on Networking and Services, (ICNS 2013), Lisbon, pp. 193-199, March 2013.

- [11] AM335x ARM Cortex-A8 Microprocessors, Technical Reference Manual p. 5.2.5. [Online]. Available: <u>https://s3-us-west-1.amazonaws.com/123d-circuits-datasheets/uploads%2F1378501288</u> <u>286-gibpl1belakmx6r-2561e976ef65a4ecf67b3a3ba2590088 %2FAM</u> <u>335x\_ARM\_Cortex-A8%28spruh73h%29.pdf</u>

Proc. of the International Conference on Applied Innovations in IT, (ICAIIT), Volume 2, Issue 1, March 2014

# Efficiency Comparison of DFT/IDFT Algorithms by Evaluating Diverse Hardware Implementations, Parallelization Prospects and Possible Improvements

Danijela Efnusheva, Natasha Tagasovska, Aristotel Tentov, Marija Kalendar SS. Cyril and Methodius University - Faculty of Electrical Engineering and Information Technologies Rugjer Boshkovik bb, PO Box 574, 1000 Skopje, Macedonia E-mail: <u>{danijela, ntagasovska, toto, marijaka}@feit.ukim.edu.mk</u>

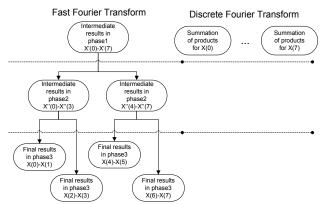

Abstract—In this paper we investigate various algorithms for performing Fast Fourier Transformation (FFT)/Inverse Fast Fourier Transformation (IFFT), and proper techniques for maximizing the FFT/IFFT execution speed, such as pipelining or parallel processing, and use of memory structures with pre-computed values (look up tables - LUT) or other dedicated hardware components (usually multipliers). Furthermore, we discuss the optimal hardware architectures that best apply to various FFT/IFFT algorithms, along with their abilities to exploit parallel processing with minimal data dependences of the FFT/IFFT calculations. An interesting approach that is also considered in this paper is the application of the integrated processing-in-memory Intelligent RAM (IRAM) chip to high speed FFT/IFFT computing. The results of the assessment study emphasize that the execution speed of the FFT/IFFT algorithms is tightly connected to the capabilities of the FFT/IFFT hardware to support the provided parallelism of the given algorithm. Therefore, we suggest that the basic Discrete Fourier Transform (DFT)/Inverse Discrete Fourier Transform (IDFT) can also provide high performances, by utilizing a specialized FFT/IFFT hardware architecture that can exploit the provided parallelism of the DFT/IDF operations. The proposed improvements include simplified multiplications over symbols given in polar coordinate system, using sine and cosine look up tables, and an approach for performing parallel addition of N input symbols.

*Keywords:* Cooley-Tukey, DFT/IDFT, FFT/IFFT, Intelligent RAM, look up tables, OFDM, pipeline and parallel processing, polar coordinate system.

#### I. INTRODUCTION

The Fast Fourier Transform and the Inverse Fast Fourier Transform are widely used efficient and fast techniques for computing the Discrete Fourier Transform and the Inverse Discrete Fourier Transform, respectively. The reduced number of FFT/IFFT calculations required for performing the same set of DFT/IDFT objectives, results in decreasing the execution complexity from  $O(N^2)$  to  $O(Nlog_2N)$ , on algorithmic level [1][2]. Consequently, FFT/IFFT modules are extensively used for analysis and implementations of communication systems with real-time data transmission requirements. Additionally, the recent advances in chip production technologies, as well as in FFT/IFFT algorithms, have resulted with production of several FFT/IFFT chips

that allow significant processing speed up (multi Gb/s) [3]-[6], as well as decreased chip area and reduced energy consumption [7]-[9].

The most important and used FFT/IFFT application is the orthogonal frequency division multiplexing (OFDM), which is the dominant transmission technique used in the 802.11 set of WLAN standards [10]. This advanced modulation technique divides the available spectrum into many overlapping subcarriers, thus allowing more effective channel utilization and reducing inter-symbol interference (ISI) and inter-carrier interference (ICI) caused by multipath effect [11].

IFFT/FFT modules execute the main functionality in OFDM systems on sending/receiving side, allowing signals to be converted from frequency/time domain to time/frequency domain [2]. Actually, the process of modulation of the subcarriers in the channel with symbol information and making them orthogonal to each other is performed by means of IFFT on the sending side, whereas the FFT is used for efficient demodulation of the received signal. By including the IFFT and FFT modules in OFDM systems, the signal processing complexity is reduced (at both, transmitting and receiving side) and higher transmission rates are achieved.

Efficient FFT/IFFT implementation is a topic of continuous research in the recent years [3][4], and the main goal is reducing the processing complexity of the FFT/IFFT calculations. In general, there are two directions in this area of research. The first one refers to developing algorithms for FFT/IFFT and their optimization. Best known algorithms in this field, worth mentioning in this paper are radix-2, radix-4, radix-8 and split-radix variations of the Cooley-Tukey (C-T) algorithm [12][13] as well as Winograd algorithm [14] By increasing the base in C-T algorithm, the number of operations is decreased, resulting in FFT/IFFT split-radix implementation becoming superior compared to Winograd algorithm [15]. The second approach is focused on hardware architecture improvements and optimization of the FFT/IFFT module. This includes adequate techniques for parallel processing and pipelining, memory structures for preservation of previously calculated results, as well as

dedicated components (usually multipliers) for more rapid calculations [16][17].

The FFT/IFFT implementation, in order to obtain better performances, can be achieved with various hardware components, including digital signal processors (DSPs), general purpose processors (GPPs), smart memories (IRAM), application specific integrated circuits (ASICs) or specialized circuits implemented on FPGA. The research has shown that GPPs and DSPs [14] are programmable and flexible, but cannot completely satisfy the fast processing requirements. On the other hand, the IRAM architecture is insufficiently explored, but considering its abilities to provide high memory bandwidth and strided memory accesses, it is expected to provide promising results [18]. Most of the FFT/IFFT implementations are realized as specialized logic circuits, characterized with different forms of parallel computing. FPGA components are utterly suitable for implementation of this type of circuits, providing a tradeoff between speed, cost, flexibility and programmability [2][6][15][16][19].

The aim of this paper is to investigate various algorithms for FFT/IFFT computation and to discuss their hardware implementation that mostly satisfies the high speed processing requirements. Actually we talk about several parallelization techniques and methods, emphasizing the problem of data dependences in the FFT/IFFT calculations that limit the processing speed and the maximal utilization of the available hardware resources. Therefore, we suggest that the basic DFT/IDFT calculations are very suitable for parallelization, which can be further improved by implementing several optimizations of the addition and multiplication operations over complex numbers. In order to be effective, the provided modifications should be supported by а specialized processor-in-memory architecture. Initial ideas for implementing such approach, are presented in this paper.

This paper is organized in five sections. Section two discusses variety of FFT/IFFT algorithms for fast calculation of the DFT/IDFT and compares their efficiency. Section three provides an overview of different FFT/IFFT hardware implementations, discussing the achievable speed up by introducing parallelism. Section four presents several techniques for efficient hardware implementation of the basic DFT/IDFT computations, as well as possible DFT/IDFT improvements of the multiplication and addition operations, which are essential for performing the summation of products in the DFT/IDFT. The proposed improvements should involve maximal parallelism, during the execution of the DFT/IDFT computations. The paper ends with a conclusion, stated in section five.

#### II. SOFTWARE OPTIMIZATION OF DISCRETE FOURIER TRANSFORM

The DFT/IDFT is the most important discrete transform, used to perform Fourier analysis in many practical applications. For example, it has a fundamental function for modulation and demodulation in OFDM systems [2]. This transformation deals with a finite discrete-time signal and a finite or discrete number of frequencies, so it can be implemented in computers by numerical algorithms or even -vector dedicated hardware. Given n real or complex inputs  $x_0, ..., x_{n-1}$ , the DFT [2] [20], is defined as:

$$y_k = \sum_{0 \le \ell < n} \chi_\ell \omega_n^{-k\ell}, \ 0 \le k < n, \tag{1}$$

with  $\omega_n = \exp(-2\pi i/n)$  and  $i = \sqrt{-1}$ . Stacking  $y_k$  and  $\chi_\ell$  into vectors  $x = (x_0, ..., x_{n-1})^T$  and  $y = (y_0, ..., y_{n-1})^T$  yields into the equivalent form of a matrix-vector product:

$$y = DFT_n x, \ DFT_n = [\omega_n^{kl}], 0 \le k, l > n$$

(2)

Straightforward computation of both DFT and convolution is a matrix-vector multiplication, given as  $W \bullet \overrightarrow{g}$  and takes  $O(N^2)$  operations, for N being a transformation size.

The breakthrough of the Cooley-Tukey algorithm's family derives from its capability of significantly cutting down DFT's  $O(N^2)$  complexity to an order of  $O(Nlog_2N)$ , [13]. This advance in computational theory inspired and motivated a stream of researches targeting even further speed up and efficiency of performing DFT, and eventually a whole new class of algorithms was introduced, known as FFT algorithms. A common feature for most FFT algorithms is their order of complexity -  $O(Nlog_2N)$ .

### *A.* Divide and Conquer Approach as a Basis for FFT Algorithms

The DFT usually arises as an approximation to the continuous Fourier transform, allowing functions sampling at discrete intervals in space or time. In order to make the DFT operation more practical, several FFT algorithms were proposed. The fundamental approach for all of them is to make use of the properties of the DFT operation itself, and thus reduce the computational cost of performing the DFT calculations. This is basically achieved by implementing the divide and conquer approach [21], which is a basis for most of the algorithms for effective computation of DFT.

We already stated that the discrete Fourier transform is a matrix product, whereas  $x_0, ..., x_{N-1}$  is the vector of input samples,  $x = (X_0, ..., X_{N-1})^T$  is the vector of transform values and  $W_N$  is the primitive N<sup>th</sup> root of unity, so that  $W_N = \exp(-2\pi i / N), i = \sqrt{-1}$  [20]. This product is given by the following equation:

$$\begin{bmatrix} X_{0} \\ X_{1} \\ X_{2} \\ X_{3} \\ \vdots \\ X_{N-1} \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 & 1 & \cdots & 1 \\ 1 & W_{N} & W_{N}^{2} & W_{N}^{3} & \cdots & W_{N}^{N-1} \\ 1 & W_{N}^{2} & W_{N}^{4} & W_{N}^{6} & \cdots & W_{N}^{N(N-1)} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ 1 & W_{N}^{N-1} & W_{N}^{2(N-1)} & \cdots & \cdots & W_{N}^{(N-1)(N-1)} \end{bmatrix} \times \begin{bmatrix} x_{0} \\ x_{1} \\ x_{2} \\ x_{3} \\ \vdots \\ x_{N-1} \end{bmatrix}$$

(3)

$W_N$  is also referred to as the *twiddle factor* or *phase factor*. This value being a trigonometric function over discrete points around the 4 quadrants of a two dimensional plane, has symmetric and periodic properties [22]. Using these properties of the twiddle factor, unnecessary computations of the DFT can be easily eliminated.

The direct evaluation of the matrix-vector product requires  $N^2$  complex multiplications and additions. In order to reduce this huge number of operations, a divide and conquer approach is implemented. The general idea of this methodology is to map the original problem into several sub-problems in such a way that the following inequality, [20], is assured:

#### cost(subproblems) + cost(mapping) < cost(original problem) (4)

The real influence of this method is that, regularly, the division can be applied recursively to the sub-problems as well, thus leading to a reduction of the order of complexity.

The important point in (4) is that the divide and conquer scheme is consisted of two clear costs: the cost of the mapping (which can be zero when looking at the number of operations only) and the cost of the sub-problems. As a consequence, different types of divide and conquer methods make an effort to find balancing schemes between the mapping and the sub-problem costs [20]. As an example, the Cooley-Tukey radix-2 algorithm can be considered, where the sub-problems results being quite trivial (only sum and differences), although the mapping requires twiddle factors that lead to a large number of multiplications. On the contrary, in the prime factor algorithm, the mapping is done only by means of permutations (no arithmetic operation are required), while the small DFTs that appear as sub-problems indicate substantial costs since their lengths are co-prime numbers.

#### B. Families of FFT Algorithms

There are two core families of FFT algorithms: the Cooley-Tukey algorithms and the Prime Factor algorithms, [20]. These classes of algorithms differ in the way they translate the full FFT into smaller sub-transforms. Mostly two types of routines for Cooley-Tukey algorithms are used: mixed-radix (general-N) algorithms and radix-2 (power of 2) algorithms. All Radix algorithms are similar in structure, differing only in the core computation of the butterflies, [23]. Each type of algorithm can be further categorized according to additional features, such as whether it operates in-place or requires an additional scrape space, whether its output is in a sorted or scrambled order, and whether it uses decimation-in-time or -frequency iterations.

#### 1) Cooley-Tukey Algorithms

The Cooley–Tukey set of algorithms comprises the most common fast Fourier transform (FFT) algorithms. They reexpresses the discrete Fourier transform (DFT) of an arbitrary composite size  $N = N_1N_2$  in terms of smaller DFTs of sizes  $N_1$  and  $N_2$ , recursively, in order to reduce the computation time to  $O(Nlog_2N)$  for highly-composite N (smooth numbers). Usually, either  $N_1$  or  $N_2$  is a small factor (not necessarily prime), called the radix (which can differ between stages of the recursion) [20]-[23]. If  $N_1$  is the radix, the Cooley–Tukey algorithm is called decimation in time (DIT), whereas if  $N_2$  is the radix, it is decimation in frequency (DIF).

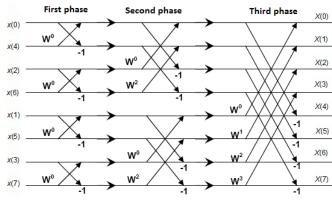

A radix-2 DIT FFT is the simplest and most common form of the Cooley–Tukey algorithm, although highly optimized Cooley–Tukey implementations generally use some other forms of the algorithm. Radix-2 DIT decomposes a DFT of size N into two interleaved DFTs (hence the name "radix-2") of size N/2 with each recursive stage, eventually resulting in a combining stage containing only size-2 DFTs called "butterfly" [13], operations (so-called because of the shape of the data-flow diagrams, Fig. 1).

Fig. 1. Flow graph of 8-point DIT FFT radix-2 Cooley-Tukey algorithm.

Besides the radix-2 Cooley-Tukey algorithm, other implementations with radixes of 4 and 8 are also used. Actually, the value of the radix (2, 4, 8) indicates that the total number of points used for the transformation can be expressed as  $2^x$ ,  $4^x$  or  $8^x$ , accordingly [15]. Therefore, the C-T algorithm can execute parallel and independent butterfly operations with 2, 4 or 8 input/output values, in each of the algorithm phases (for radix x, the number of phases is  $\log_x N_y$ ).

Mixed-radix (also called split-radix) algorithms work by factorizing the data vector into smaller lengths. These can then be transformed by FFTs with small number of points, noted as small-N FFT [24]. Typical programs include FFTs for small prime factors, such as 2, 3 or 5, which are highly optimized. Actually, the idea of this algorithm is to use many multiplied small-N FFT modules and combine them in order to make longer transforms. If the small-N modules are supplemented by an  $O(N^2)$  general-N module then an FFT of any length can be computed. Of course, any lengths which contain large prime factors would perform only as  $O(N^2)$ .

The well-known radix-2 Cooley–Tukey algorithm is a simplified version of the mixed-radix algorithm, realized by the use of FFT modules whose lengths are only power of two. Radix-2 algorithms have been the subject of much research into optimizing the FFT. Many of the most efficient radix-2 routines are based on the "split-radix" algorithm [15]. This is actually a hybrid which combines the best parts of both radix-2 ("power of 2") and radix-4 ("power of 4") algorithms, for computing distinctive partitions of the Fourier's transformation.

#### 2) Prime Factor Algorithms

The prime-factor algorithm (PFA), (also known as the Good–Thomas algorithm), is a FFT algorithm that reexpresses the DFT of a size  $N = N_1N_2$  as a two-dimensional  $N_1 \times N_2$  DFT, but only for the case where  $N_1$  and  $N_2$  are relatively prime. These smaller transforms of size  $N_1$  and  $N_2$  can then be evaluated by applying PFA recursively or by using some other FFT algorithm. Although this algorithm has a very simple indexing scheme, it only works in the case where all factors are co-prime, which makes it suitable as a specialized algorithm for given lengths, [25]. PFA is also closely related to the nested Winograd FFT algorithm, where the latter performs the decomposed  $N_1$  by  $N_2$  transform via more sophisticated two-dimensional convolution techniques [26]. Winograd algorithm is requiring the least known number of multiplications among practical algorithms for moderate lengths DFTs.

Another less known algorithm is Fast Hartley Transform (FHT) [27]. This effective algorithm cannot be classified in formally presented families, since its core characteristic is what moves them apart. For the DFHT, the kernel is real, unlike the complex exponential kernel of the DFT. For complex data, each complex multiplication in the summation requires four real multiplications and two real additions using the DFT. For the DFHT, this computation involves only two real multiplications and one real addition.

It can be noticed that performing efficient and fast discrete Fourier transform, truly inspired researchers and burst many peoples' creativity. Sequentially, along with many ideas, came many experiments, evaluations and analysis. An effort was made to sum up the general conclusions in terms of complexity (meaning effectiveness) of the different types of FFT algorithms. Table 1 and Table 2 present the results.

From the results gathered in Table 1 and Table 2, an assumption can be made, that in general, split-radix algorithm achieves best performance. However, its irregular structure introduces some difficulties during the implementation [15]. Observing Table 1, another thing can be noticed, and that is the obvious decrement of the number of operations required for FFT, with each increment of algorithms' radix. Regarding the Prime Factor Algorithms, from Table 2 it can be concluded that Winogard is more efficient for smaller FFT sizes while for FFTs with input array sizes grater then 500 points, Prime Factor Algorithms present better results. Thus, for this family of algorithms a general winner or leading algorithm cannot be determined.

At this stage, we conclude FFT algorithms brief overview and efficiency evaluation, considering different manners of influencing DFT performances' only through algorithms, i.e. optimization in software. Nevertheless, these influences' impact depends on the characteristics of the platform the algorithms are executed on. Thus, this paper elaborates the FFT algorithms possible hardware implementations in section 3, as well.

#### C. FFT Parallelization and Optimization in Software

The emergence of multi-core processors also encouraged further research and optimization of FFT algorithms. The most popular of the previously discussed algorithms were rewritten introducing multi-threaded FFT programs. However, well known rule of thumb is that, the more the code is optimized, the harder it is to be realized in parallel. Most researches in this direction go with sequentially executing code until a parallel region is reached where multiple threads can be employed, [28]. This practice is truly more a need, since FFT algorithms' separate stages depend on each other's results.

An accent was also put on joint resources, like twiddle factors and bit reversal mapping which are commonly presented as lookup tables (LUT) [28][29]. But then again, memory may be saved, but usually the case is that memory accesses are far more expensive (in terms of speed of execution) then arithmetic operations, due to slower memories. The consequence of this type of implementation may not be the performance one hoped for. This particular fact was the starting point for the FFTW project, [30], where an effort was made for maximum utilization of computers' fast memory (cache and RAM), by introducing selfoptimizing FFT algorithms on the behalf of specialized compiler, that adapt themselves in the form most suitable for particular architecture implementation. Sdalksdf

### III. HARDWARE OPTIMIZATION OF FFT ALGORITHMS IMPLEMENTATIONS

Efficiency comparison on all previously discussed algorithms makes no real sense if they are not associated with their hardware application. By hardware, we mean certain architecture and particular platform. It was proven that the desired performance requirements will only be met if FFT algorithms are applied into suitable hardware set. Architectures vary in number of available processing units as well as in memory size and distribution. These two main features have inevitable impact on FFT algorithms efficiency, since they cover parts of FFT which proved to be the most intense – arithmetic operations and memory accesses.

## *A.* Various Platforms for FFT Algorithms Hardware Implementations

Several architectures have been proposed [31][32], each of them trying to optimize the load of memory accesses and increase overall speed of FFT execution. These architectures effectiveness can be further evaluated by physical implementation. Today's cutting edge technology provides number of hardware platforms fit for deploying FFT algorithms. In this paper GPP, DSP as well as specialized hardware circuits – ASIC and FPGAs implementations are discussed.

TABLE I

COMPARISON OF MULTIPLICATION AND ADDITION COMPLEXITY OF DFT and Cooley-Tukey Based FFT/IFFT Algorithms

DFT

C-T Radix-8

C-T Split Radix

|            | DFT          |              |         |              | C-T Radix    | -2    | С            | -T Radix     | -4    | С            | -T Radix     | -8    | C            | -T Split R   | adix  |

|------------|--------------|--------------|---------|--------------|--------------|-------|--------------|--------------|-------|--------------|--------------|-------|--------------|--------------|-------|

| Poin<br>ts | Real<br>Adds | Real<br>Muls | Total   | Real<br>Adds | Real<br>Muls | Total | Real<br>Adds | Real<br>Muls | Total | Real<br>Adds | Real<br>Muls | Total | Real<br>Adds | Real<br>Muls | Total |

| 16         | 992          | 1024         | 2016    | 152          | 24           | 176   | 148          | 20           | 168   |              |              |       | 148          | 20           | 168   |

| 32         | 4032         | 4096         | 8128    | 408          | 88           | 496   |              |              |       |              |              |       | 388          | 68           | 456   |

| 64         | 16256        | 16384        | 32640   | 1032         | 264          | 1296  | 976          | 208          | 1184  | 972          | 204          | 1176  | 964          | 196          | 1160  |

| 128        | 65280        | 65536        | 130816  | 2504         | 712          | 3216  |              |              |       |              |              |       | 2308         | 516          | 2824  |

| 256        | 261632       | 262144       | 523776  | 5896         | 1800         | 7696  | 5488         | 1392         | 6880  |              |              |       | 5380         | 1284         | 6664  |

| 512        | 1047552      | 1048576      | 2096128 | 13576        | 4360         | 17936 |              |              |       | 12420        | 3204         | 15624 | 12292        | 3076         | 15368 |

| 1024       | 4192256      | 4194304      | 8386560 | 30728        | 10248        | 40976 | 28336        | 7856         | 36192 |              |              |       | 27652        | 7172         | 34824 |

| COMPA  | COMPARISON OF MULTIPLICATION AND ADDITION COMPLEXITY OF DFT AND PRIME FACTOR BASED FFT/IFFT ALGORITHMS |              |         |              |              |       |              |              |       |  |  |  |  |

|--------|--------------------------------------------------------------------------------------------------------|--------------|---------|--------------|--------------|-------|--------------|--------------|-------|--|--|--|--|

|        |                                                                                                        | DFT          |         |              | Prime Facto  | r     |              | Winograd     |       |  |  |  |  |

| Points | Real<br>Adds                                                                                           | Real<br>Muls | Total   | Real<br>Adds | Real<br>Muls | Total | Real<br>Adds | Real<br>Muls | Total |  |  |  |  |

| 60     | 14280                                                                                                  | 14400        | 28680   | 888          | 200          | 1088  | 888          | 136          | 1024  |  |  |  |  |

| 240    | 229920                                                                                                 | 230400       | 460320  | 4812         | 1100         | 5912  | 5016         | 632          | 5648  |  |  |  |  |

| 504    | 1015056                                                                                                | 1016064      | 2031120 | 13388        | 2524         | 15912 | 14540        | 1572         | 16112 |  |  |  |  |

| 1008   | 4062240                                                                                                | 4064256      | 8126496 | 29548        | 5804         | 35352 | 34668        | 3548         | 38216 |  |  |  |  |

TABLE II

Architectural and design issues which are to be considered for diverse FFT hardware implementations are: precision of data, number of points for FFT size, and memory usage. Then performance evaluation is done according to power consumption, required circuit board area and desired circuit frequency. The value of these variables depends on the application which makes use of FFT i.e. employs it, and what's even more is that these same parameters have impact on the whole system (FFT algorithm + platform) performances.

#### 1) General Purpose Processors

Many research efforts have been performed in this area [30][33] being just part of it. What is interesting to notice is that a greater part of the execution time was spent on load and store operations, compared to actual arithmetic computations [20]. This is a straightforward consequence of the GPP architecture, designed to satisfy many diverse applications' needs. Thus, from all implementations, this has proven to be the least effective one. Nevertheless researches utilizing these platforms continue, since many upper layer applications, using everyday technology (consisting GPPs) require FFT. Hence, a great advancement is made with the FFTWs' development, which provides an opportunity for one to choose an optimal algorithm for particular GPP, due to its adaptive features, by benchmarking FFTW library. From the gathered results it is obvious that for different FFT size, different platform is more convenient.

#### 2) Digital Signal Processors

DSPs offer the best flexibility, but limited performance. These processors sturdily service multiply/accumulate based algorithms. Unluckily, this is not the case of any FFT algorithm (where sums of products have been changed to fewer but less regular computations) [20]. Still, DSPs now meet some of the FFT requirements, like modulo counters and bit-reversed addressing. If the modulo counter is general, it will help the implementation of all FFT algorithms, but it is often restricted to the Cooley-Tukey/SRFFT case only (modulo a power of 2), for which proficient timings are provided on nearly all available machines by manufacturers, at slightest for small to medium lengths. DSPs achieve low development cost compared to dedicated hardware solutions, although at the expense of medium performance and high power consumption.

#### 3) Application Specific Integrated Circuit

Application Specific Integrated Circuits are famous for being the fastest platform for processing intense operations. Many hardware product vendors like Xilinx and Altera accepted this appropriateness of using ASIC chips for FFT implementations, and have developed high performance IP cores, from which designers benefit in reducing the time required for various product development. Compared to GPU and DSP they provide flexibility in terms of algorithms, meaning they are convenient not only for traditional Cooley-Tukey algorithms but also for PFA, [34]. Another reason to use them is their power efficiency requirements which are lowest of all.

#### 4) Field Programmable Gateway Arrays (FPGA)

Fast Fourier transform has been playing an important role in digital signal processing and wireless communication systems, so the choice of FFT sizes is decided by different operation standards. It is anticipated to make the FFT size configurable according to the operation environment, since achieving a successful design means the system should be able to support different operating modes required by diverse applications with low power consumption requirement [35]. This is the reason why reconfigurable hardware has been paid more attention recently. FPGAs combine ASICs desired speed of operation with the flexibility provided from DSP, resulting in a perfect match for FFT implementations. Additionally, the capability of changing the source code according to current specific application makes this type of platform convincing winner for FFT implementation. Despite of all the upsides, a disadvantage must be mentioned, and that its power consumption.

Further, this paper presents another not so explored platform, but from our point of view, suitable for FFT implementation, and that is Intelligent RAM–IRAM.

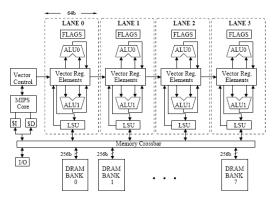

#### 5) Intelligent RAM

Intelligent RAM [18], is another merged DRAM-logic processor, designed at the Berkeley University of California by a small Patterson's team of students. This chip was designed to serve as multimedia processor on embedded devices. As a result of the design studies of the Berkeley's team research group, it was shown that most applicable architecture to multimedia processing is vector architecture, rather than MIND, VLIW, and other ILP organizations [36]. This is basically because of the vector processors' abilities to deliver high performance for data-parallel tasks execution, and to provide low energy consumption, simplicity of implementation and scalability with the modern CMOS technology.

The resulted IRAM chip is called Vector IRAM (VIRAM). VIRAM is processor that couples on-chip DRAM for high bandwidth with vector processing to express fine-grained data parallelism [18]. The VIRAM architecture (shown on Fig. 2) consists of MIPS GPP core, attached to a vector register file that is connected to an external I/O network and also to a 12MB DRAM memory organized in 8 banks.

Fig. 2. Architecture of IRAM chip.

FFT computations are difficult to be realized with conventional GPP architectures, given that they require high memory bandwidth and strided memory accesses. Nevertheless, it was shown that the performance of computing floating-point FFTs on a VIRAM processor, [18], can be competitive with that of existing floating point DSPs and specialized fixed-point FFT chips.

From this section it can be concluded that there is no such thing as a universally optimal FFT/IFFT algorithm, architecture and implementation that is appropriate for all systems. Therefore, it is recommended to perform a search across the algorithm, architecture and implementation dimensions for each system.

## *B.* Further FFT Speedup by Introducing Parallelization Techniques in Hardware

Traditional FFT hardware architectures include trade-offs among complexity, power consumption, die size, and other similar parameters. Still, these architectures don't have the scalability to encounter high speed processing requirements on FFT performance, for instance on emerging high data rate technologies in wireless communications, like OFDM. Progress in technology empowers development of architectures optimal for given class of algorithms, including FFT.

In general, there are three main techniques of improving overall FFT speed, all of them based on the Transpose algorithm, described in [37]:

1) Increasing the order of the radix.

This approach improves both latency and throughput, but is expensive in terms of computational resource required for each processing unit.

- Cascading (pipelining) the processors. Different processors operate over different stages. Cascading improves throughput, but not latency. Inter stage memory is necessary.

- 3) Parallelizing the processors. Parallelizing the processors, so that a single large FFT is divided into N smaller FFTs. Both latency and throughput are improved with this arrangement. Drawback is the data transfer between stages.

All these improvement methods require architecture modifications. Thus, in literature, commonly two architecture approaches are presented: memory-based FFT and pipeline-based FFT. Memory-based FFT uses only one butterfly and large memories for data storage. On the other hand, pipelined architecture uses many butterflies to improve the speed. There are several FFT hardware modules that have been proposed to implement both methods (memory-based design and pipelined design) in order to improve speed and minimize area. For example, [38] proposes six memory-based implementations, realized in FPGA. The authors give the name of RX2-B1, RX4-B1, RX2-B2, RX4-B2, RX2-B4, MXRX-B4 for these architectures, whereas the RX presents the used radix and Bi indicates that the architecture operates with i outputs in parallel. The techniques used for each of these architectures are based on memory sharing, conflict free memory addressing, in-place memory processing, continuous flow design, N-word memory size, fixed-point arithmetic and pre-computed twiddle factors stored in ROM. It was found that the fastest processors are the RX2-B4 and MXRX-B4 FFT models which can process four data samples per clock cvcle.

Another direction in researching memory based architecture is towards distributed memory and processing units. This technique requires re-expressing the FFT algorithms to adapt them for parallel implementation. According to [21][39], where several algorithms were tested, it was proven that additional complexity is added to the system, as a consequence of the need for communication between different modules. Also, it was noticed that not all algorithms are suitable for parallelization, since only algorithms with regular structure (Cooley-Tukey Radix-2/4, Split Radix) are advisable, while the block complexity of Winograd algorithm makes it difficult and unsuited for parallel implementation.

Regarding the pipelined architectures, many works have presented optimizations to achieve high performance and low area consumption. The most famous architectures of pipeline implementations are multi-path delay commutator, radix-2 single path delay commutator and radix-2 single path delay feedback, [35]. The main difference between these architectures is in the number of inputs, outputs and butterflies used.

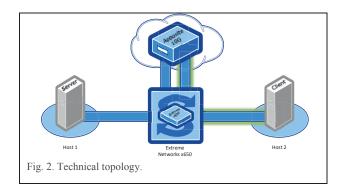

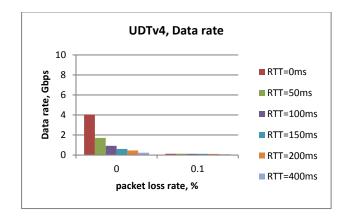

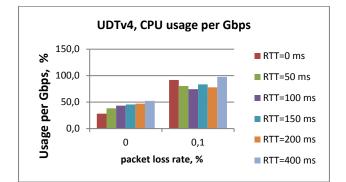

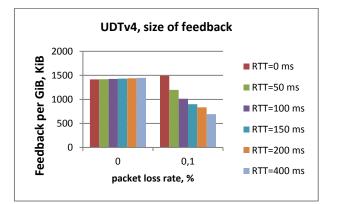

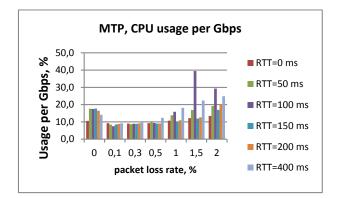

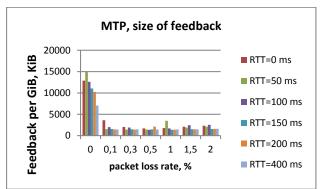

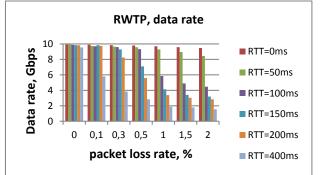

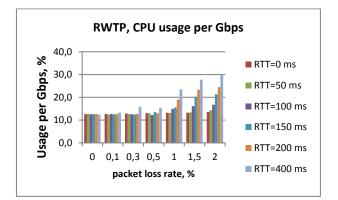

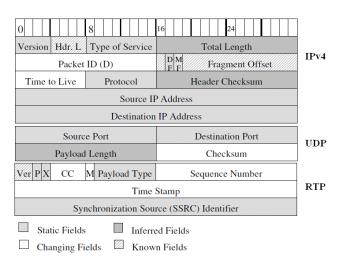

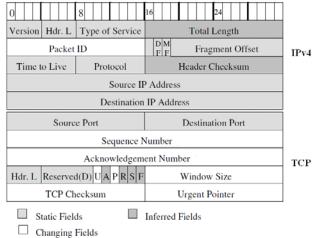

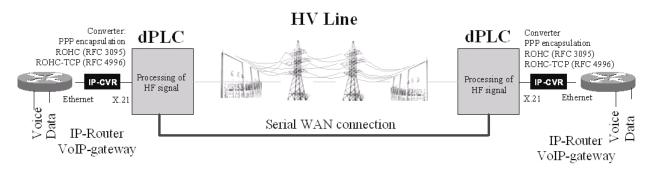

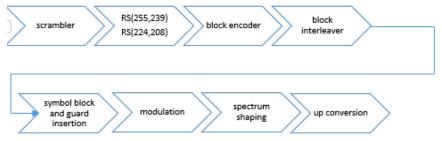

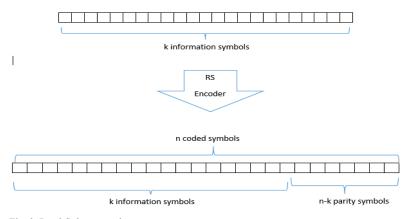

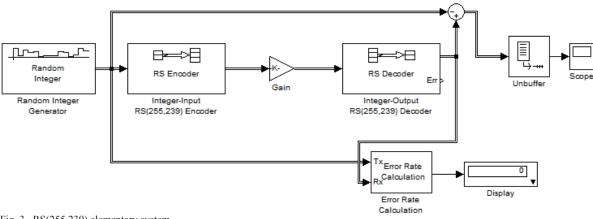

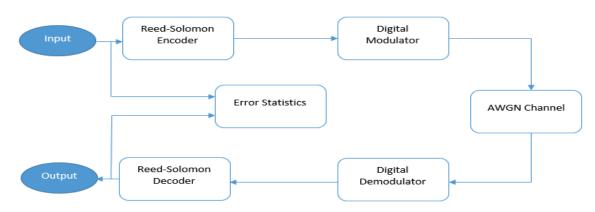

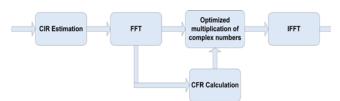

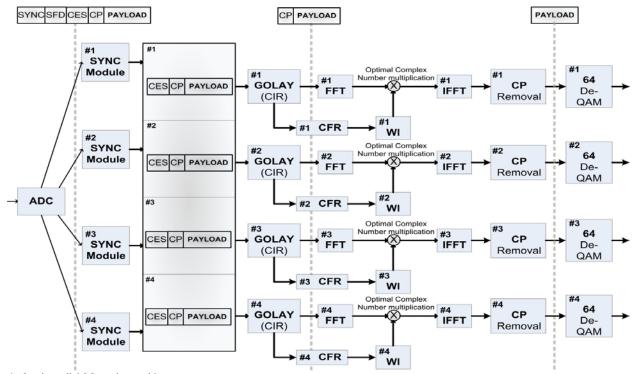

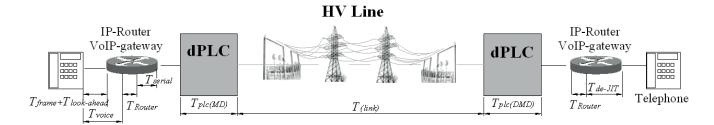

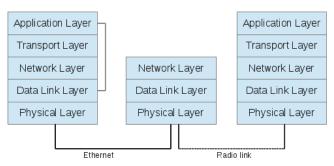

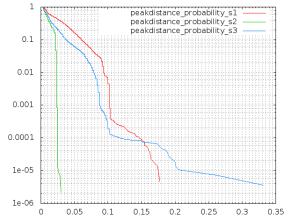

A different approach is applied by [40] proposing an array processing architecture for parallel FFT implementation. Key advantage of this architecture is the elimination of inter stage data transfer, so both, the system throughput and latency are improved. This idea is basically similar to IRAM, [18], which also includes vector processing units, capable to process the input data in parallel.